#### **Discontinued Product—Support Information Only**

This literature was published years prior to the establishment of Agilent Technologies as a company independent from Hewlett-Packard and describes products or services now available through Agilent. It may also refer to products/services no longer supported by Agilent. We regret any inconvenience caused by obsolete information. For the latest information on Agilent's test and measurement products go to:

#### www.agilent.com/find/products

Or in the US, call Agilent Technologies at 1-800-452-4844 (8am-8pm EST)

# HP 64785A Emulator for Hitachi SH7032 and 7034 Microprocessors

# **Product Overview**

The HP 64785A active probe emulator supports Hitachi SH7032 and SH7034 microprocessors up to 20 MHz.\* This emulator supports SH7032/34 processors in 5-V versions. The system offers the realtime measurement capabilities needed to develop SH7032/34 embedded systems, including interpreted displays of on-chip registers, emulation memory, a deep-trace analyzer, and hardware break events.

HP's host-independent emulation and analysis systems can be controlled from a simple terminal, HP 9000 workstations, or Sun SPARCstations. Access to these systems is through a selection of user interfaces, including an X/Motif-based embedded debug environment for HP workstations and Sun SPARCstations. This allows you to open several emulation and analysis windows for simultaneous display during a session, providing visibility on several parameters at once.

\* Contact your HP 64000 field engineer for the latest configuration information and supported processor speeds. Design, debug, and integrate real-time embedded systems

**Agilent Technologies**

#### Features

- No-wait state execution up to 20 MHz\*

- Support for SH7032 and 7034 processors

- Configuration menu for easy emulator setup

- Display and modify functions for internal I/O registers

- Background monitor

- Eight real-time hardware break events

- Unlimited software execution breakpoints

- Support for the fast file download

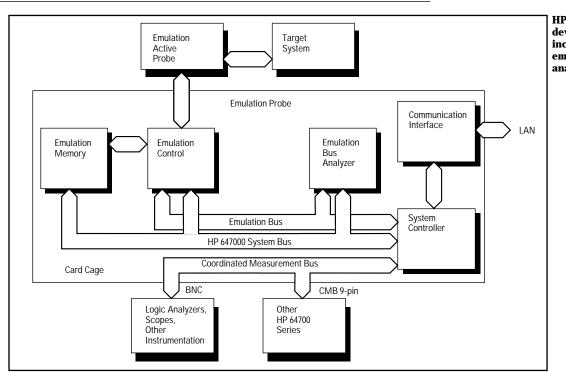

- Termination to a 112-pin QFP package

- Three-foot probe cable terminating in an active probe

- Flexible probing to target system by 9-inch QFP flexible cable

- QFP socket adapter, soldered

on target system, for both the emulator probe and a QFP real chip

- Memory for internal RAM/ROM and monitor support configurations without an optional emulation memory module for a single chip application

- Simulated I/O (on workstation)

- Cross-triggering between another emulator, logic analyzer, or oscilloscope

- Support for Hitachi compiler and assembler on HP 9000/700 and Sun SPARCstations

- Support for Green Hills Software, Inc. compiler and assembler on HP 9000/700, Sun SPARCstations, and IBM PC compatibles

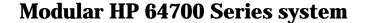

HP 64700 Series development tools include emulators and emulation bus analyzers.

#### **Emulation Bus Analyzer**

- 80 channels available with trace buffer depths of 1 K, 8 K, 64 K, or 256 K

- Postprocessed software-based dequeued trace with symbols and source lines

- Eight events, each consisting of address, status, and data comparators that can be sequenced up to 8 levels deep

- Time tag with 20-ns resolution (64794x) and state counts

- Prestore capability

#### **Emulation Memory**

- One-state access up to 20 MHz (HP 64172A/B)

- One-state access up to 16.6MHz and two-state access above 16.6 MHz (HP 64173A/B)

- Display and modification of emulation memory with minimum processor interruption by the quick break of background monitor

- 256-KB, 1-MB and 4-MB memory configurations

- Mapping resolution of 16-KB for 64172A, 32 KB for 64172B, and 128 KB for 64173A

#### **Software Support**

• Real-time operating system measurement tools

#### **Card Cage**

The card cage is the basis for modular emulators and analyzers. It can be disassembled easily for cost-saving reconfiguration to support 8-, 16-, and 32-bit processors.

The card cage host control card contains LAN capability, along with RS-232-C/RS-422 serial port and system configuration firmware. System, emulation, and analysis firmware are always resident and may be updated.

#### Networking

In many embedded design environments, it is not possible for each member of a design team to have a target system and an emulator, which makes remote access from a networked host essential. The HP 64700 Series emulators offer a LAN connection so that you can share a central emulator and target from either a PC or a workstation.

In addition, the rapid file transfers—rates of up to 6 MB per minute—increase your productivity. The card cage connects to all popular Ethernet/803.2 networks through a 10Base2 ThinLAN BNC connector or a 15-pin AUI (attachment unit interface). The system supports TCP/IP protocols, LAN gateways, and ARPA/Berkeley standards.

2

#### **Emulation Bus Analysis**

Emulation bus analysis provides real-time, nonintrusive operation along with extensive triggering, tracing, and qualification features. Analysis features include selective tracing, time-tagging, prestore, and a selection of 1-K, 8-K, 64-K, or 256-K trace depths . These comprehensive resources combine to help you solve both simple and complex problems.

The dual-bus architecture results in real-time, nonintrusive analysis. You can set up and review traces without breaking processor execution. Selective tracing of microprocessor code flow without breaking execution is a major strength of the HP 64700 Series emulators and analyzers.

You can combine up to eight hardware breakpoint resources, each consisting of address, data, and status event comparators, in sequential trace specifications using "find A, followed by B..." constructs up to eight levels deep. Apply a range comparator to address or data events at any one of these levels. The analyzer will trigger on and store all subsequent executions or store only specified execution information.

Precise time-tagging of events helps you identify discrepancies in code execution. The analyzer logs each event with its execution time. Bus cycle, instruction, and module duration can be measured at full processor speeds.

Prestore helps you pinpoint possible problem areas in your code, by determining which of several different functions is accessing a variable and is responsible for corrupting it.

#### **Real-Time Emulation**

The HP 64785A contains the microprocessor, emulation monitor, run-control circuits, and up to 4 MB emulation memory. This emulator includes a background monitor, which uses no target address space. The background monitor can display and modify emulation memory with minimum processor interruption by the quick break, typically 200 or  $300 \mu s$ .

HP high-speed emulation memory provides you with no-wait state real- time execution, one-state memory access, which is a significant feature of SH7032 and 7034 microprocessors. HP 64172A 256-KB and HP 64172B 1-MB emulation memory support one-stateaccess up to the maximum speed, 20 MHz. HP 64173A 4-MB emulation memory supports it up to 16.6 MHz and two-state access above 16.6 MHz.

Extensive breakpoint capabilities are included, allowing you to define where to stop code execution. Software breakpoints can be set up in the emulator, allowing execution to be halted at an instruction point.

Real-time hardware break events increase the flexibility and power of this feature, extending functionality to include stopping at a processor address, data, status points, or a combination of all three.

#### Flexible Memory Configuration

Memory modules provide emulation memory. One slot is available on the active probe, allowing you to plug in the amount of memory you need up to 4 MB. If you initially order less than the maximum amount, you can easily expand by replacing it with the appropriate module. Modules for 256 KB (HP 64172A), 1 MB (HP 64172B), and 4 MB (HP 64173A) are available.

#### **Symbolic Support**

Symbolic debugging clarifies trace-list interpretation by allow-

ing you to see program symbols in the trace list. This feature facilitates quick identification of problems involving the interaction of software and hardware. You can also use symbols in emulation commands and expressions to simplify command entries and user interaction.

#### Workstation-Hosted Environment

The HP embedded debug environment is an emulator/analyzer user interface for software development.

The emulator/analyzer tool gives you the ability to perform trace analysis, set breakpoints, and establish emulator configuration parameters. In addition, the graphical interface tool is integrated with the embedded debug environment, which coordinates high-level microprocessor run control.

The HP debug environment supports language tools from Hitachi and Green Hills Software, Inc., which provide software tools compatible with the HP 64785A emulator. Both toolsets include C cross-compiler and an assembler.

#### **Terminal Mode Operation**

A firmware-resident ASCII terminal interface is embedded in the emulator, supplying commands for all emulation and analysis features. Commands are ASCII strings; the system accepts file transfers using industry-standard formats. Because a terminal can access these commands, host independence is realized.

## **HP 64785A Emulator Specifications**

| Model HP 64785A:                           |                                                                                                                           |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Hitachi SH7032/34 ir                       | n 5 V version                                                                                                             |

| Electrical                                 |                                                                                                                           |

| Maximum<br>Clock Speed:                    | 20 MHz* with no-wait<br>states required for<br>emulation or target                                                        |

| one-state access u<br>emulation memory     | system memory.<br>lation memory supports<br>p to 20 MHz. HP 64173A<br>supports one-state access<br>two-state access above |

| Minimum<br>Clock Speed:                    | 2MHz                                                                                                                      |

| Power:                                     | Primary power supplied by card cage                                                                                       |

| Environmental                              |                                                                                                                           |

| Temperature:                               | Operating, 0 to +40 °C<br>(+32 to +104 °F)<br>Non-operating, -40 to<br>+60 °C (-40 to 140 °F)                             |

| Altitude:                                  | Operating, 4600 m<br>(15,000 ft)<br>Non-operating, 15300                                                                  |

| m                                          | (50,000 ft)                                                                                                               |

| Regulatory Complia<br>when installed in HI | nce<br>P 64700 card cage                                                                                                  |

| Electromagnetic<br>A                       | EN55011 Group1 Class                                                                                                      |

| Interference:                              |                                                                                                                           |

| Safety:                                    | Self-certified to<br>UL 1244, IEC 348,<br>CSA-231                                                                         |

| Physical                                   |                                                                                                                           |

| Cable length:                              | Probe to card cage approximately 1 m                                                                                      |

| (40")                                      |                                                                                                                           |

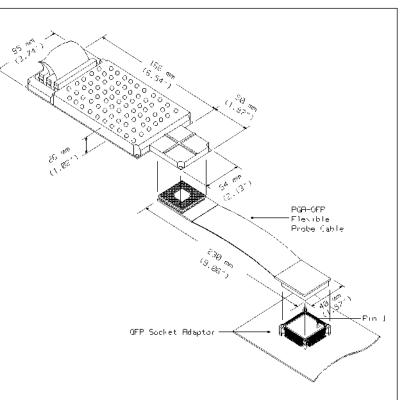

**Notice for the QFP Socket Adapter** The QFP socket adapter is an expendable supply because the electrical contacts degrade gradually as the flexible probe cable is attached and detached. One QFP socket adapter is supplied with HP 64785A. Please prepare some spares of the QFP socket adapter in advance. The part number is HP 64784-61611.

64785A Dimensions

**QFP Socket Adapter Dimensions**

4

## HP 64785A AC Timing **Specifications: 20MHz**

| Characteristic                 | Symbol | SH7     | /034   | HF     | 9 64785 | A         | Characteristic                                         | Symbol         | SH70    | 3  |

|--------------------------------|--------|---------|--------|--------|---------|-----------|--------------------------------------------------------|----------------|---------|----|

|                                |        | 20 1    | ИНz    | Worst  | Case    | Typical   |                                                        |                | 20 M    | Η  |

|                                |        | Min     | Max    | Min    | Max     | (*1)      |                                                        |                | Min     |    |

| EXTAL input high-level pulse   | tEXH   | 10 ns   |        |        |         | 10 ns     | Parity output delay time 1                             | tWPDD1         |         |    |

| EXTAL input low-level pulse    | tEXL   | 10 ns   |        |        |         | 10 ns     | Parity output delay time 2                             | tWPDD2         |         |    |

| EXTAL input rise time          | tEXr   |         | 5 ns   |        |         | 5 ns      | Parity output hold time                                | tWPDH          | 0 ns    |    |

| EXTAL input fall time          | tEXf   |         | 5 ns   |        |         | 5 ns      | Wait setup time                                        | tWTS           | 14 ns   | ĺ  |

| Clock cycle time               | tcyc   | 50 ns   | 500 ns |        |         | 50,500 ns | Wait hold time                                         | tWTH           | 10 ns   |    |

| Clock high-pulse width         | tCH    | 20 ns   |        |        |         | 24 ns     | Read data access time 1                                | tACC1          | 20 ns   |    |

| Clock low-pulse width          | tCL    | 20 ns   |        |        |         | 18 ns     | Read data access time 2                                | tACC2          | 70ns    | L  |

| Clock rise time                | tCr    |         | 5 ns   |        |         | 4 ns      | RAS delay time 1                                       | tRASD1         |         |    |

| Clock fall time                | tCf    |         | 5 ns   |        |         | 4 ns      | RAS delay time 2                                       | tRASD2         |         |    |

| Reset oscillation setting time | tOSC1  | 10 ms   |        | 10 ms  |         | 10 ms     | CAS delay time 1                                       | tCASD1         |         | 7  |

| Software standby oscillation   | tOSC2  | 10 ms   |        | 10 ms  |         | 10 ms     |                                                        |                |         | 4  |

| setting time                   |        |         |        |        |         |           | CAS delay time 2                                       | tCASD2         |         | F  |

| RESET setup time               | tRESS  | 200 ns  |        | 250 ns |         |           | CAS delay time 3                                       | tRASD3         |         |    |

| RESET pulse width              | tRESW  | 20 t cy | с      |        | 20 t c  | VC        | Column address setup time                              | tCAC1          | Ons     | L  |

| NMI reset setup time           | tNMIRS | 200 ns  | -      | 235 ns |         | ,-        | CAS to read data access time 1                         | tCAC1          | 13.5ns  |    |

| NMI reset hold time            | tNMIRH | 200 ns  |        | 200 ns |         |           | (35% duty)                                             |                |         |    |

| NMI setup time                 | tNMIS  | 100 ns  |        | 110 ns |         |           | CAS to read data access time 1                         | tCAC1          | 6ns     | l  |

| NMI hold time                  | tNMIH  | 50ns    |        | 50 ns  |         |           | (50% duty)                                             |                |         | l  |

| IRQ0-IRQ7 setup time           | tIRQES | 100 ns  |        | 110 ns |         |           | CAS to read data access time 2                         | tCAC2          | 25 ns   |    |

| (edge detection time)          |        |         |        |        |         |           | RAS to read data access time 1                         | tRAC1          | 55 ns   | ĺ  |

| IRQ0-IRQ7 setup time           | tIRQLS | 100 ns  |        | 110ns  |         |           | RAS to read data access time 2                         |                | 105 ns  | l  |

| (level detection time)         |        |         |        |        |         |           | High-speed page                                        | tCP            | 12.5 ns |    |

| IRQ0-IRQ7 hold time            | tIRQEH | 50 ns   |        | 50 ns  |         |           | mode CAS precharge time 1                              |                |         | L  |

| IRQOUT output delay time       | tIRQOD |         | 50 ns  |        | 50 ns   |           | AH delay time 1                                        | tAHD1          |         | i  |

| Bus request setup time         | tBRQS  | 50ns    |        | 55 ns  |         |           | AH delay time 2                                        | tAHD2          |         | :  |

| Bus acknowledge delay time 1   | tBACD1 |         | 50 ns  |        | 55 ns   |           | Multiplexed address delay time                         | tMAD           |         | :  |

| Bus acknowledge delay time 2   | tBACD2 |         | 50 ns  |        | 55 ns   |           | Multiplexed address hold time                          | tMAH           | 0 ns    |    |

| Bus 3-state delay time         | tBZD   |         | 50 ns  |        | 55 ns   |           | DACK0-DACK1 delay time 1                               | tDACD1         |         | 1  |

| Address delay time             | tAD    |         | 20 ns  |        | 30 ns   | 13 ns     | DACK0-DACK1 delay time 2                               | tDACD2         |         | :  |

| CS delay time 1                | tCSD1  |         | 25 ns  |        | 30 ns   | 10 ns     | DACK0-DACK1 delay time 3                               | tDACD3         |         | 1  |

| CS delay time 2                | tCSD2  |         | 25 ns  |        | 30 ns   | 6 ns      | DACK0-DACK1 delay time 4                               | tDACD4         |         |    |

| CS delay time 3                | tCSD3  |         | 20 ns  |        | 25 ns   |           | DACK0-DACK1 delay time 5<br>Read delay time (35% duty) | tDACD5<br>tRDD |         |    |

| CS delay time 4                | tCSD4  |         | 20 ns  |        | 25 ns   |           | 27 ns                                                  | INDD           |         | 4  |

| Access time 1 from             | tRDAC1 | 12.5 ns | 6      | 2.5 ns |         | 12.5 ns   | Read delay time (50% duty)                             | tRDD           |         | 1  |

| read strobe (35% duty)         |        |         |        |        |         |           | Data setup time for CAS                                | tDS            | 0 ns    | ſ  |

| Access time 1 from             | tRDAC1 | 5 ns    |        | -5 ns  |         | 5 ns      | CAS setup time for RAS                                 | tCSR           | 10 ns   | F  |

| read strobe (50% duty)         |        |         |        |        |         |           | Row address setup time                                 | tRAH           | 10 ns   | Ĺ  |

| Access time 2 from             | tRDAC2 | 62.5 ns | 6      | 52.5ns |         | 62.5 ns   | Write command hold time                                | tWCH           | 15 ns   |    |

| read strobe (35% duty)         |        |         |        |        |         |           | Write command setup time                               | tWCS           | 0 ns    |    |

| Access time 2 from             | tRDAC2 | 55 ns   |        | 45 ns  |         | 55 ns     | (35% duty)                                             | 10003          | 0115    |    |

| read strobe (50% duty)         |        |         |        |        |         |           | -                                                      | tWCS           | 0 ns    |    |

| Read strobe delay time         | tRSD   |         | 20 ns  |        | 25 ns   | 8 ns      | (50% duty)                                             | 10005          | 0115    | l. |

| Read data setup time           | tRDS   | 15 ns   |        | 25 ns  |         | 15 ns     |                                                        |                |         |    |

| Read data hold time            | tRDH   | 0ns     |        | 0ns    |         | 0 ns      | *1 Typical outputs measured wit                        | (n 50 pF 10    | ad      |    |

| Write strobe delay time 1      | tWSD1  |         | 20 ns  |        |         | 10 ns     |                                                        |                |         |    |

| Write strobe delay time 2      | tWSD2  |         | 20 ns  |        | 25 ns   |           |                                                        |                |         |    |

| Write strobe delay time 3      | tWSD3  |         | 20 ns  |        | 25 ns   | 11ns      |                                                        |                |         |    |

| Write strobe delay time 4      | tWSD4  |         | 20 ns  |        | 25 ns   |           |                                                        |                |         |    |

| Write data delay time 1        | tWDD1  |         | 35 ns  |        | 40 ns   | 21 ns     |                                                        |                |         |    |

| Write data delay time 2        | tWDD2  |         | 20 ns  |        | 40ns    | 23 ns     |                                                        |                |         |    |

| Write data hold time           | tWDH   | 0 ns    |        | -5 ns  |         | 2 ns      |                                                        |                |         |    |

5

SH7034

20 MHz

Max

40 ns

20 ns

20ns

30ns

20ns

20ns

20ns

20 ns

20 ns

30 ns

23 ns

23 ns

20 ns

20 ns 20 ns

29.5 ns

40 ns

HP 64785A

Max

45 ns

25 ns

25ns 8ns

35ns

25ns

25ns 9ns

25ns 8ns

24 ns

11 ns

3 ns

10 ns

10 ns 20 ns

70ns

14ns

6ns

13ns

13.5ns

6ns

25 ns

55 ns

105 ns

24 ns

6 ns

25 ns 6 ns

25 ns 8 ns

35 ns 16 ns

28ns

28 ns

25 ns 25 ns

25 ns 34.5 ns

45ns 35ns

6 ns

19 ns

20 ns 31 ns

7 ns

14 ns

Min

-5 ns

24 ns

10 ns

5 ns 55ns

-5ns

3.5ns

-4ns

15 ns

45 ns

95 ns

-5 ns

-5 ns

5 ns

5 ns

10 ns

-5 ns

-5 ns

Worst Case |Typical (\*1)

### **Ordering Information**

| Model     | Description                                         |

|-----------|-----------------------------------------------------|

| 64785A    | 20-MHz active probe emulator with space for up to   |

|           | 4 MB of emulation memory for SH7032/34 processors   |

|           | (includes demo board, 112-pin QFP flexible cable,   |

|           | and QFP socket adapter)                             |

| 64748C    | Emulation control card                              |

| 64794A    | 8K-deep emulation bus analyzer card, 80 channels    |

| 64700B    | Card cage                                           |

| Emulation | System Options                                      |

| Model     | Description                                         |

| 64172A    | 256 KB, SRAM memory module (20 ns)                  |

| 64172B    | 1 MB, SRAM memory module (20 ns)                    |

| 64173A    | 4 MB, SRAM memory module (25 ns)                    |

| 64704A    | 1 K-deep 80-channel emulation bus analyzer card     |

| 64794C    | 64 K-deep emulation bus analyzer card, 80 channels  |

| 64794D    | 256 K-deep emulation bus analyzer card, 80 channels |

| 64023A    | CMB cable (4 m; includes three 9-pin connectors)    |

#### **Software Options**

For each software model number ordered, purchase one media option and at least one license option for each concurrent user:

| <b>Model</b><br>B3076B | <b>Description</b><br>Graphical user interface      |  |  |  |

|------------------------|-----------------------------------------------------|--|--|--|

| Media/License Options  |                                                     |  |  |  |

| opt AAH                | HP 9000 Series 300/400 manuals/media (DDS DAT tape) |  |  |  |

| opt AAX                | HP 9000 Series 300/400 manuals/media                |  |  |  |

| -                      | (1/4 inch cartridge tape)                           |  |  |  |

| opt UBX                | HP 9000 Series 300/400 single-user license          |  |  |  |

| opt AAY                | HP 9000 Series 700 manuals/media (DDS DAT tape)     |  |  |  |

| opt UBY                | HP 9000 Series 700 single-user license              |  |  |  |

| opt AAV                | Sun SPARCstation manuals/media                      |  |  |  |

| -                      | (1/4 inch cartridge tape)                           |  |  |  |

| opt UBV                | Sun SPARCstation single-user license                |  |  |  |

| <b>a a</b>             | · · · · · · · · · · · · · · · · · · ·               |  |  |  |

Software Support

HP provides software upgrades through the purchase of the software materials subscription (SMS) service. Contact your HP field engineer for more information.

For more information on Hewlett-Packard Test & Measurement products, applications or services please call your local Hewlett-Packard sales offices. A current listing is available via Web through AccessHP at http://www.hp.com If you do not have access to the internet please contact one of the HP centers listed below and they will direct you to your nearest HP representative.

United States: Hewlett-Packard Company Test and Measurement Organization 5301 Stevens Creek Blvd. Bldg. 51L-SC Santa Clara, CA 95052-8059 1 800 452 4844

Canada: Hewlett-Packard Canada Ltd. 5150 Spectrum Way Mississauga, Ontario L4W 5G1 (905) 206 4725

Europe: Hewlett-Packard European Marketing Centre P.O. Box 999 1180 AZ Amstelveen The Netherlands

Japan: Hewlett-Packard Japan Ltd. Measurement Assistance Center 9-1, Takakura-Cho, Hachioji-Shi, Tokyo 192, Japan Tel: (81-426) 48-0722 Fax: (81-426) 48-1073

Latin America: Hewlett-Packard Latin American Region Headquarters 5200 Blue Lagoon Drive 9th Floor Miami, Florida 33126 U.S.A. (305) 267 4245/4220

Australia/New Zealand: Hewlett-Packard Australia Ltd. 31-41 Joseph Street Blackburn, Victoria 3130 Australia 131 347 ext. 2902

Asia Pacific: Hewlett-Packard Asia Pacific Ltd 17-21/F Shell Tower, Times Square, 1 Matheson Street, Causeway Bay, Hong Kong (852) 2599 7070

Technical information in this document is subject to change without notice

Printed in the U.S.A. 12/95 5963-9986E